# SCADAMETRICS

# Bell 202 Modem

FOR RADIO TELEMETRY

#### **Standards-Based, Non-Proprietary Modem** For Radio Telemetry...

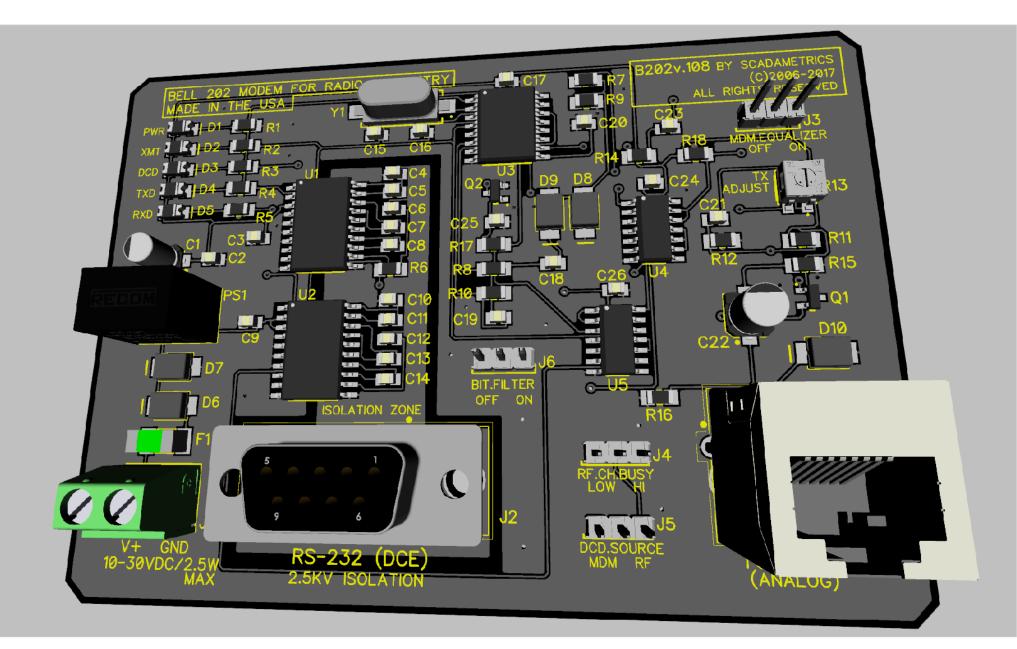

The SCADAmetrics Model B202 Modem is designed to provide non-proprietary, Bell-202 data modulation and demodulation for many popular analog telemetry radios.

The unit offers the following notable features:

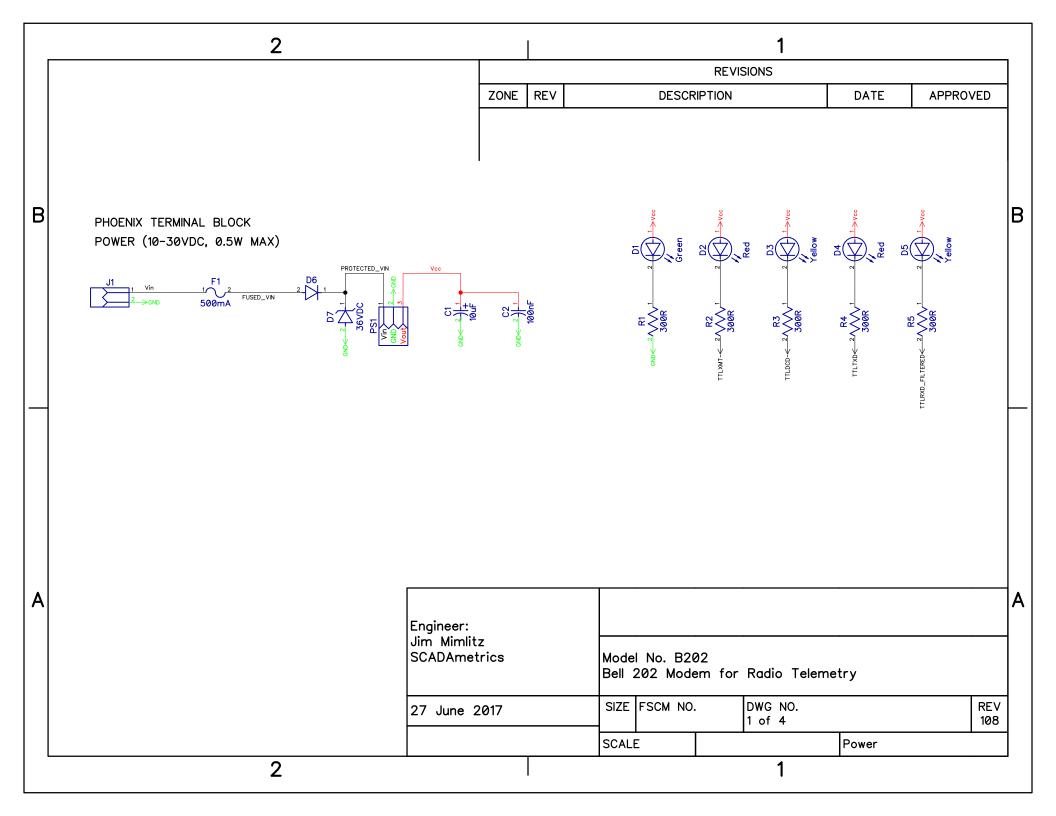

- Wide-Input Power Range 10-30VDC.

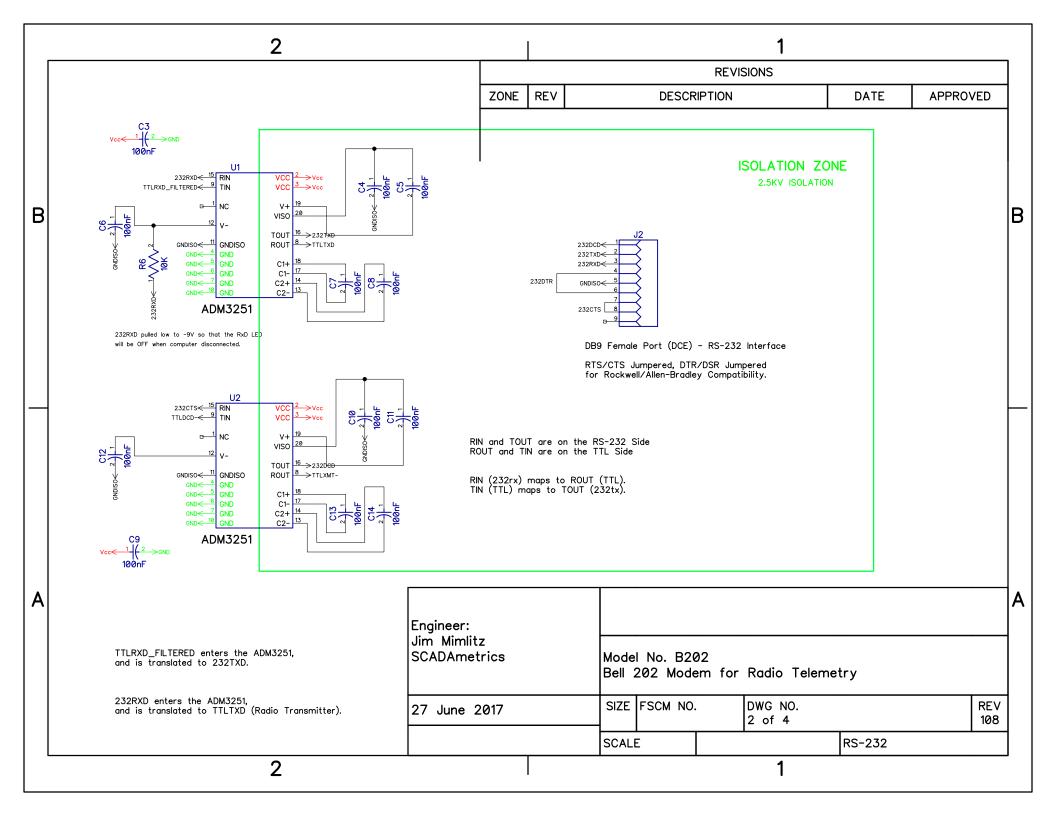

- 2.5KV Isolated Serial Port for RS-232 Interface to PLC/RTU/Computer.

- Serial Port Pins 4-6, 7-8 Jumpered for Rockwell/Allen Bradley Compatibility.

- Radio Interface: RJ45F.

- Industrial Din-Rail Mount.

- LED's: Power, Transmit, Receive, TxD, RxD.

- Adjustable Transmit Audio Level: 0-2V Peakto-Peak Signal. Able to Drive 600-∞ Ω Loads.

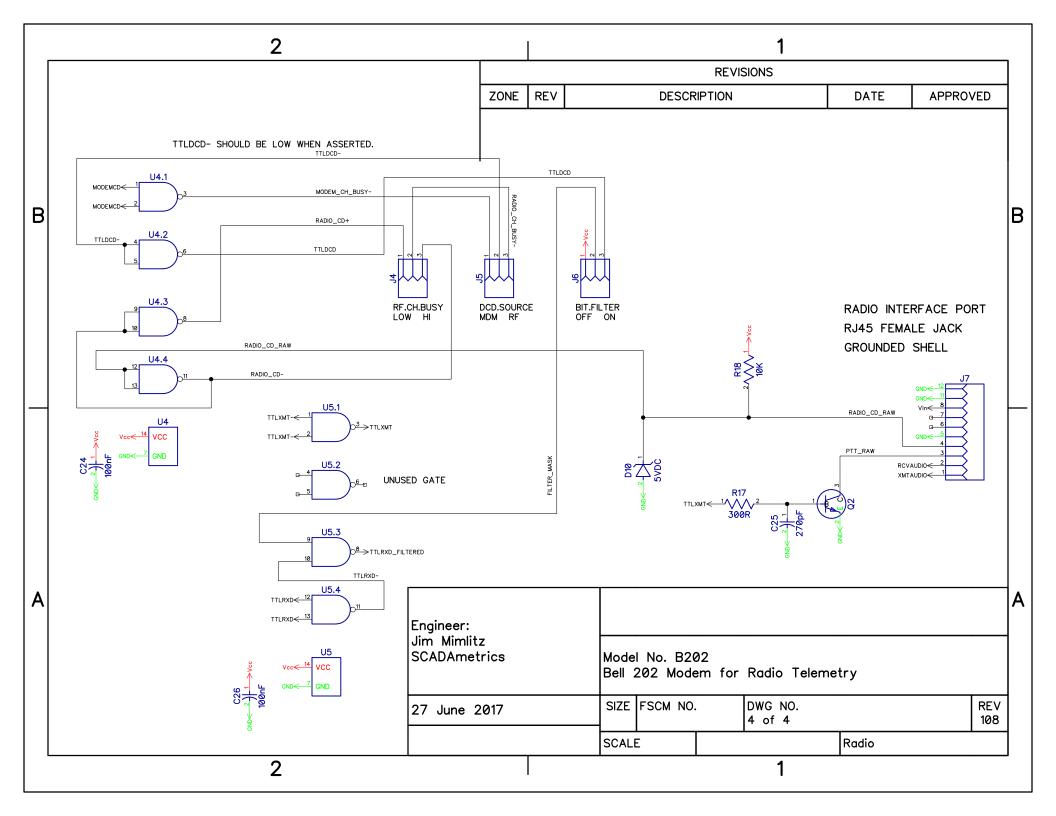

- Selectable RF or Modem Carrier Detect.

- Carrier-Detect Byte Filtering Option.

- Receive Signal Equalizer Option.

- 'Dumb' Mode Operation.

The B202 modem permits users to mix various makes and models of compatible radios within a telemetry system, thereby alleviating the problem of vendor lockin.

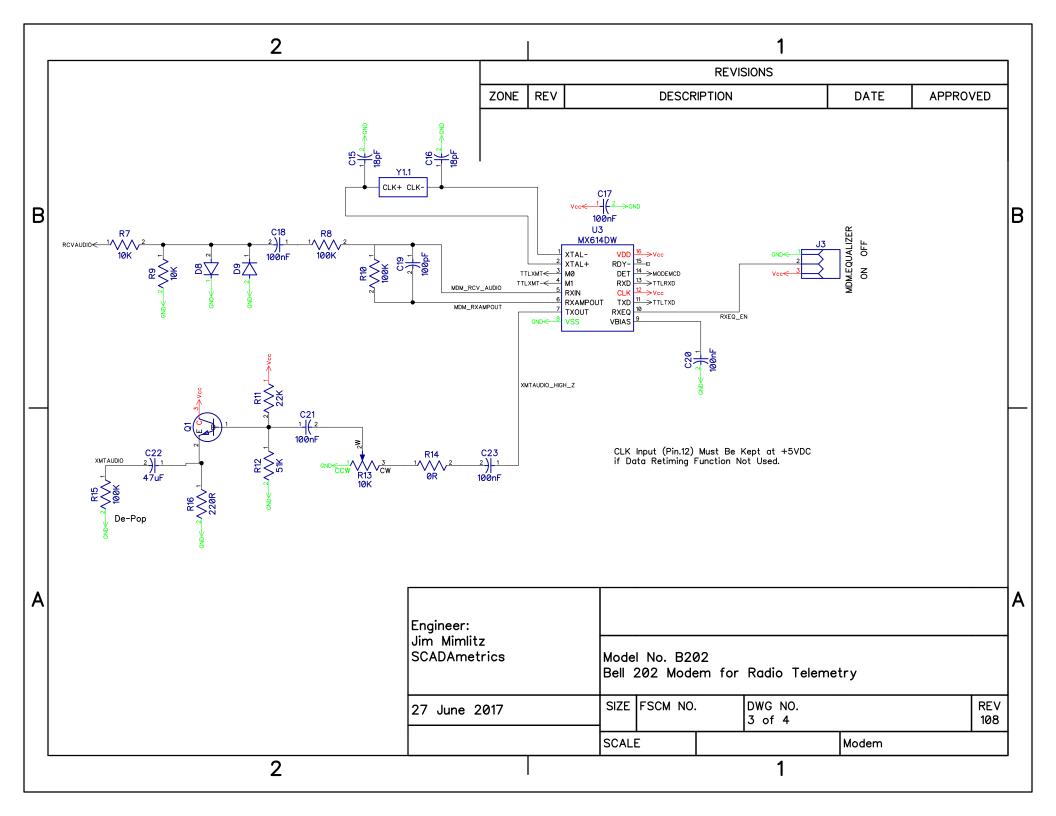

This new design is based upon the MX614 modem IC (CML Micro), and it is also fully compatible with legacy Bell-202 modems that are based upon the TCM3105 modem IC (Texas Instruments), such as the Calamp DM-3282, Maxon SD-FSK, and MARC 366-101. Compatibility is anticipated with a wide range of popular analog telemetry radios, including models from the following manufacturers:

- Ritron

- Tecnet / Maxon

- GE / Microwave Data Systems

- Calamp

- RF Neulink

In accordance with FCC CFR 47 Part 15.103(a,b,c) – the B202 is only intended to be used as a control system component at public utility facilities, industrial plants, and within commercial transportation vehicles. It is also intended to be used within industrial, commercial, & medical test equipment. Not intended for consumer applications.

SCADAmetrics scadametrics.com St. Louis, Missouri USA (636)405-7101

# Specifications...

#### Mechanical/Electrical

Manufacturing Location: Dimensions: Weight: Temperature: Relative Humidity: Panel Mounts: Supply Voltage/Power: Supply Current:

Serial Port Isolation: Term. Blk. Conductors: Internal Power Efficiency: Circuit Protection:

Audio Output Signal Level:

3.250"

4.125"

USA

3.8 Ounces

2 5 KV

90%, Typical

600-∞ Ohm Loads.

-30C to +85C

4.125" x 3.250" x 1.750"

5% to 95%, Non-Condensing

Two (2) Universal Din-Rail Clips

Fused (375mA) + TVSS Diode +

Reverse-Polarity Protection Diode

0-2V peak-to-peak (0-.708Vrms), Adjustable.

10VDC to 30VDC, 1.50W max

100mA @ 12VDC, Typical 50mA @ 24VDC, Typical

16AWG Max, 26AWG Min

#### Serial Communications

| Interface Port: |  |

|-----------------|--|

|                 |  |

|                 |  |

1: DCD (Transmitted to DTE) 2: TxD (Transmitted to DTE) 3: RxD (Received from DTE) 4: DSR (TIED TO DTR) 5: GND 6: DTR (TIED TO DSR) 7: CTS (TIED TO DSR) 7: CTS (TIED TO RTS) 8: RTS (TIED TO CTS) 9: N/C 300 to 1200 bps None (Requires External RTS/PTT Control) MODBUS, DF1, Custom Binary & ASCII Protocols

RS-232C (DB9F Jack, DCE):

#### **Radio Communications**

Modulation Type: Interface Port:

Speed:

Handshaking:

Protocol Compatibility:

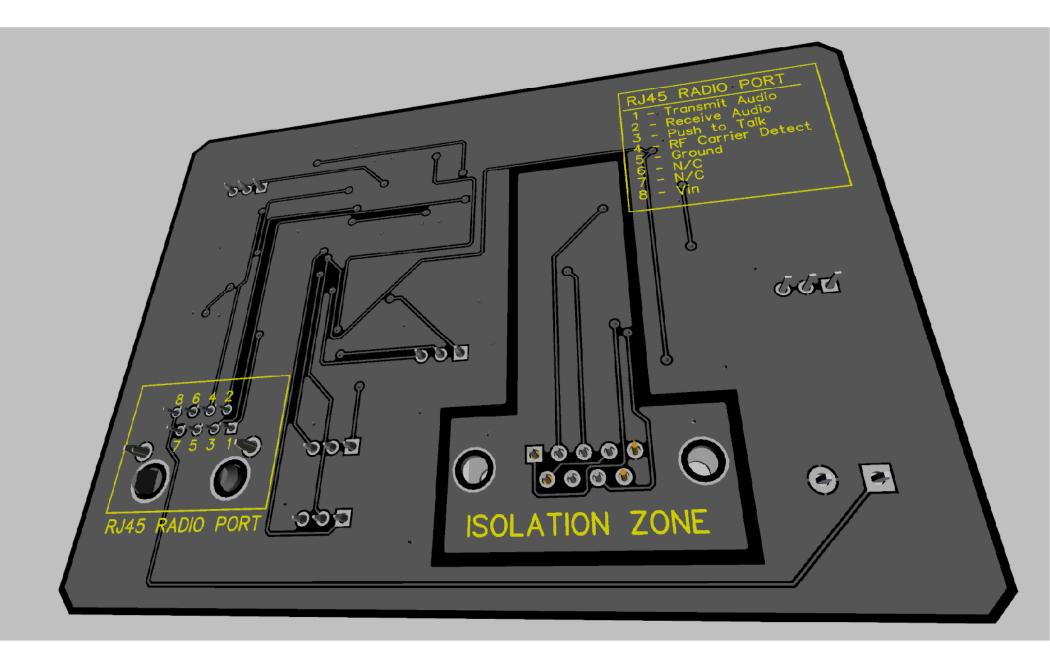

AFSK (Audio Frequency Shift Key), Bell-202 **RJ-45F:** 1: TxAudio (Adj: 0-2 Vpp / 0-0.708 Vrms) 2: RxAudio 3: PTT (Active Low) 4: Channel Busy 5: Ground 6: N/C 7: N/C 8: DC Power (Non-Fused, Mapped from V+ Terminal)

#### **Configuration Jumpers**

RF.CH.BUSY Normal (~5V=BUSY)

JP1 = HI

RF.CH.BUSY Inverted (0V=BUSY)

JP1 = LOW

(Sets Polarity of Radio Channel Busy/Carrier Detect)

DCD.SOURCE = RF Channel Busy

JP2 = RF

DCD.SOURCE = Modem Energy Detect

JP2 = MDM

(Sets The Source Of DCD Signal: Radio or Modem)

BIT.FILTER ON JP3 = ON BIT.FILTER OFF JP3 = OFF (BIT.FILTER ON: Data Only Passed Thru When DCD Asserted)

MDM.EQUALIZER ONJP4 = ONMDM.EQUALIZER OFFJP4 = OFF(Modem Equalizer – See Explanation On Page 6 of MX614 Datasheet)

# FAQ's...

• **Is the B202 a 'smart' modem?** No, the B202 modem is a 'dumb' modem. The benefits are total control of the modulation and demodulation process and enhanced ability to troubleshoot. However, a 'dumb' modem requires the user to key the transmitter through software prior to and during data transmission using the RTS serial port pin. The user also must provide logic to detect and separate valid packets from extraneous noise. This is typically done by framing each packet with a pre-determined byte sequence.

• What are the power requirements of the B202?

The B202 provides the user with a great deal of flexibility in that it will operate on any voltage between 10-30VDC. However, it is almost always preferable that the user power the modem with the same voltage source that is used to power the radio – which will generally be ~12VDC. Pin 8 of the RJ45 jack provides a direct connection back to the V+ terminal block. If the radio is to be powered with a separate voltage source, then it is imperative that Pin 8 of the RJ45 jack should <u>not</u> be connected to the radio.

• **Does the B202 require programming?** No, the unit features 4 jumpers for tailoring the modem to your radio and application, and one trim pot for adjusting the transmit audio level.

• **Do you offer radio interface cables?** Yes. Because many of the popular telemetry radios feature DB9, DB25, or DB15 interface ports; and it's now extremely easy and popular to create custom cable assemblies with RJ45F-to-DSub Adapters. This allows us to offer cable assemblies for many popular telemetry radios. Our cable assemblies generally consist of an RJ45F-DSub Adapter and a premium shielded CAT5 patch cable (24-gauge, solid-copper conductors).

• What documentation is available? The B202 is offered as a non-proprietary modem device whose operation can be troubleshot and repaired by qualified technical personnel. For this reason, complete documentation is provided – including operations manual, schematics, and the modem IC datasheet.

• What are the Bell-202 modulation tones? The Bell-202 standard uses 1200 Hz for `MARK' (Binary `1'), and 2200 Hz for `SPACE' (Binary `0').

SCADAmetrics scadametrics.com St. Louis, Missouri USA (636)405-7101

# COMMUNICATION SEMICONDUCTORS

# DATA BULLETIN

# MX614

# Bell 202 Compatible Modem

## Features

- 1200bps 1800bps half duplex Bell 202 Compatible Modem

- Optional 1200bps Data Retiming Facility can eliminate external UART

- Optional 5bps and 150bps Back Channel

- Optional Line Equalization

## PRELIMINARY INFORMATION

# Applications

- Low Voltage Operation (3.3V to 5.0V)

- Low Power Operation 1mA typ. @ 3.3V Operating Mode 1µA typ. Zero-Power Mode

- Standard 3.58MHz Xtal/Clock

- Telephone Telemetry Applications

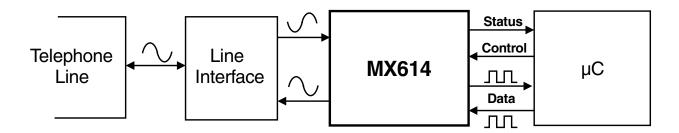

The MX614 is a low voltage, low power CMOS integrated circuit designed for the reception or transmission of asynchronous 1200bps data. This device is compatible with Bell 202 type systems. The MX614 supports 5bps and 150bps 'back channel' operation. Asynchronous data rates up to 1818bps are also supported.

The MX614 provides an optional Tx and Rx data retiming function which can eliminate, based on user preference, the need for a UART in the associated  $\mu$ C when operating at 1200bps. An optional line equalizer has been incorporated into the receive path and is controlled by an external logic level.

The MX614 may be used in a wide range of telephone telemetry systems. A very low current "Zero Power Mode (1µA typ.) and an operating current of 1mA typ. @  $V_{DD}$  = 3.3V, make the MX614 ideal for portable, terminal and line powered applications. A standard 3.58MHz Xtal/Clock is required and the device operates from a 3.0V to 5.5V supply.

The MX614 is available in 24-pin TSSOP (MX614TN), 16-pin SOIC (MX614DW) and 16-pin PDIP (MX614P) packages.

# **CONTENTS**

| Section                               | Page |

|---------------------------------------|------|

| 1. Block Diagram                      | 3    |

| 2. Signal List                        | 4    |

| 3. External Components                | 5    |

| 4. General Description                | 6    |

| 4.1 Xtal Osc and Clock Dividers       |      |

| 4.2 Mode Control Logic                | 6    |

| 4.3 Rx Input Amplifier                | 6    |

| 4.4 Receive Filter and Equalizer      | 6    |

| 4.5 Energy Detector                   | 7    |

| 4.6 FSK Demodulator                   | 7    |

| 4.7 FSK Modulator and Transmit Filter | 8    |

| 4.8 Rx Data Retiming                  | 9    |

| 4.9 Tx Data Retiming                  | 10   |

| 5. Application Notes                  | 12   |

| 5.1 Line Interface                    | 12   |

| 6. Performance Specification          | 13   |

| 6.1 Electrical Performance            | 13   |

| 6.2 Packaging                         | 16   |

MX•COM, Inc. reserves the right to change specifications at any time and without notice.

#### MX614 PRELIMINARY INFORMATION

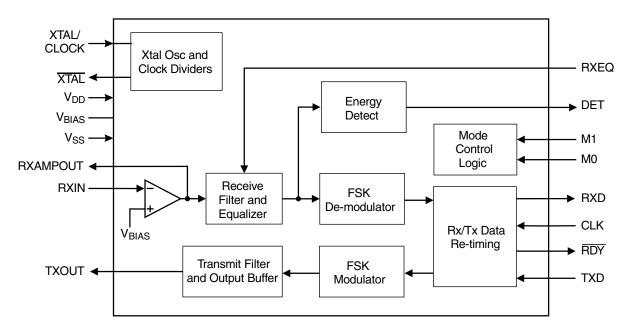

## 1. Block Diagram

Figure 1: Block Diagram

# 2. Signal List

| Pin   | No.                                        | Signal            |        | Description                                                                                                                                                                                                                                                                      |

|-------|--------------------------------------------|-------------------|--------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| P, DW | TN                                         | Name              | Туре   |                                                                                                                                                                                                                                                                                  |

| 1     | 1                                          | XTAL              | output | Output of the on-chip Xtal oscillator inverter.                                                                                                                                                                                                                                  |

| 2     | 2                                          | XTAL/CLOCK        | input  | Input to the on-chip Xtal oscillator inverter.                                                                                                                                                                                                                                   |

| 3     | 5                                          | MO                | input  | A logic level input for setting the mode of the device. See section 4.2                                                                                                                                                                                                          |

| 4     | 6                                          | M1                | input  | A logic level input for setting the mode of the device. See section 4.2                                                                                                                                                                                                          |

| 5     | 7                                          | RXIN              | input  | Input to the Rx input amplifier.                                                                                                                                                                                                                                                 |

| 6     | 8                                          | RXAMPOUT          | output | Output of the Rx input amplifier                                                                                                                                                                                                                                                 |

| 7     | 11                                         | TXOUT             | output | Output of the FSK generator.                                                                                                                                                                                                                                                     |

| 8     | 12                                         | V <sub>SS</sub>   | Power  | Negative supply (ground).                                                                                                                                                                                                                                                        |

| 9     | 13                                         | V <sub>BIAS</sub> | output | Internally generated bias voltage, held at $V_{DD}/2$ when the device is not in 'Zero-Power' mode. Should be bypassed to $V_{SS}$ by a capacitor mounted close to the device pins.                                                                                               |

| 10    | 14                                         | RXEQ              | input  | A logic level input for enabling/disabling the equalizer in the receive filter. See section 4.4                                                                                                                                                                                  |

| 11    | 17                                         | TXD               | input  | A logic level input for either the raw input to the FSK<br>Modulator or data to be re-timed depending on the state of<br>the M0, M1 and CLK inputs. See section 4.9                                                                                                              |

| 12    | 18                                         | CLK               | input  | A logic level input which may be used to clock data bits in or out of the FSK Data Retiming block.                                                                                                                                                                               |

| 13    | 19                                         | RXD               | output | A logic level output carrying either the raw output of the FSK Demodulator or re-timed characters depending on the state of the M0, M1 and CLK inputs. See section 4.8                                                                                                           |

| 14    | 20                                         | DET               | output | A logic level output of the on-chip Energy Detect circuit.                                                                                                                                                                                                                       |

| 15    | 23                                         | RDY               | output | "Ready for data transfer" output of the on-chip data retiming circuit. This open-drain active low output may be used as an Interrupt Request/Wake-up input to the associated $\mu$ C. An external pull-up resistor should be connected between this output and V <sub>DD</sub> . |

| 16    | 24                                         | V <sub>DD</sub>   | Power  | Positive supply. Levels and thresholds within the device are proportional to this voltage. Should be bypassed to $V_{SS}$ by a capacitor mounted close to the device pins.                                                                                                       |

|       | 3, 4,<br>9, 10,<br>15,<br>16,<br>21,<br>22 | N/C               |        | No internal connection                                                                                                                                                                                                                                                           |

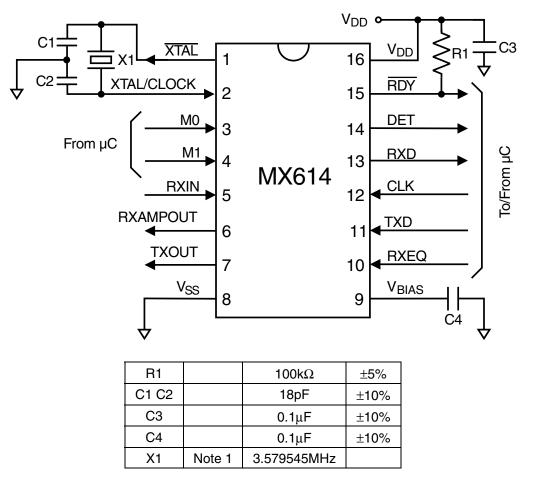

## 3. External Components

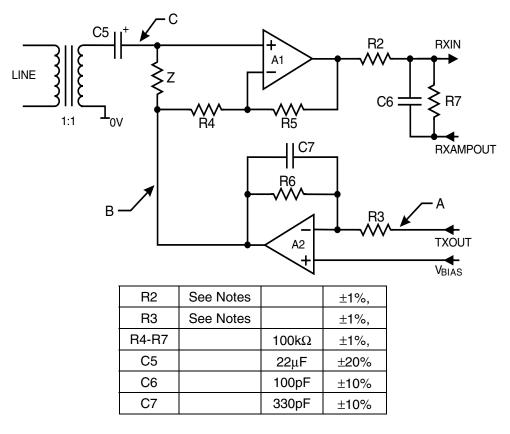

#### Figure 2: Recommended External Components for Typical Application

#### External Components Notes

- 1. **IMPORTANT:** This device is capable of detecting and decoding small amplitude signals. To achieve this  $V_{DD}$  and  $V_{BIAS}$  decoupling and protecting the receive path from extraneous in-band signals are very important. It is recommended that the decoupling capacitors be placed so that connections between them and the device pins are as short as practicable e.g.  $\leq 1$  inch from device pins. A ground plane protecting the receive path will help attenuate interfering signals

- A crystal frequency of 3.579545MHz ±0.1% is required for correct FSK operation. For best results, a crystal oscillator design should drive the clock inverter input with signal levels of at least 40% of V<sub>DD</sub> peak-peak. Tuning fork crystals generally cannot meet this requirement. To obtain crystal oscillator design assistance, consult your crystal manufacturer.

# 4. General Description

## 4.1 Xtal Osc and Clock Dividers

Frequency and timing accuracy of the MX614 is determined by a 3.579545MHz clock signal present at the XTAL/CLOCK pin. This may be generated by the on-chip oscillator inverter using the external components C1, C2 and X1 of Figure 2, or may be supplied from an external source to the XTAL/CLOCK input. If supplied from an external source, C1, C2 and X1 should not be fitted.

The on-chip oscillator is turned off in the 'Zero-Power' mode.

If the clock is provided by an external source which is not always running, then the 'Zero-Power' mode must be set when the clock is not available. Failure to observe this rule may cause a significant rise in the supply current drawn by MX614 as well as generating undefined states of the RXD, DET and RDY outputs.

## 4.2 Mode Control Logic

The MX614's operating mode is determined by the logic levels applied to the M0 and M1 input pins:

| M1       | MO             | Rx Mode | Tx Mode    | Data Retime <sup>[1]</sup> |  |  |

|----------|----------------|---------|------------|----------------------------|--|--|

| 0        | 0              | 1200bps | 150bps     | Rx                         |  |  |

| 0        | 1              | Off     | 1200bps    | Tx                         |  |  |

| 1        | 0              | 1200bps | Off / 5bps | Rx                         |  |  |

| 1        | 1              | 'Zero-l | Power'     | -                          |  |  |

| [1] If e | [1] If enabled |         |            |                            |  |  |

[1] If enabled

Note: On applying power to the device, the mode must be set to 'ZP', i.e. M0 = 1', M1 = 1', until  $V_{DD}$ has stabilized.

In the 'Zero-Power' (ZP) mode, power is removed from all internal circuitry. When leaving the 'ZP' mode there must be a delay of 20ms before any Tx data is passed to, or Rx data read from the device to allow the bias level, filters, and oscillator to stabilize.

## 4.3 Rx Input Amplifier

This amplifier is used to adjust the received signal to the correct amplitude for the FSK receiver and Energy Detect circuits (see section 5.1).

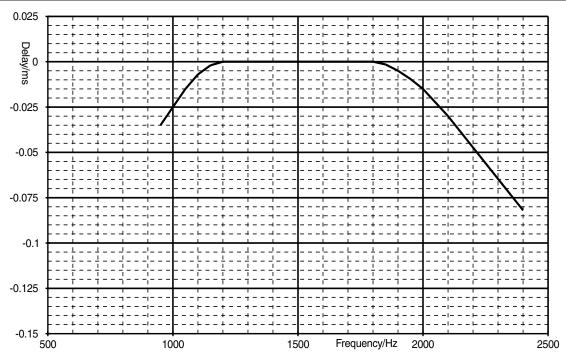

## 4.4 Receive Filter and Equalizer

The Receive Filter and Equalizer section is used to attenuate out of band noise and interfering signals, especially the locally generated transmit tones which might otherwise reach the 1200bps FSK Demodulator and Energy Detector circuits. This block also includes a switchable equalizer section. When the RXEQ pin is low, the overall group delay of the receive filter is flat over the 1200bps frequency range. If the RXEQ pin is high the receive filter's typical overall group delay will be as shown in Figure 3.

Figure 3: Rx Equalizer Group Delay (RXEQ = '1') wrt 1700Hz

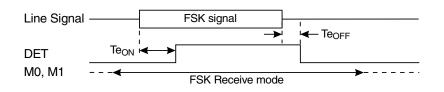

### 4.5 Energy Detector

This block operates by measuring the level of the signal at the output of the Receive Filter, and comparing it against a preset threshold.

The DET output will be set high when the level has exceeded the threshold for a sufficient period of time. Amplitude and time hysteresis are used to reduce chattering of the DET output in marginal conditions.

Note that this circuit may also respond to non-FSK signals such as speech.

See section 6.1 for definitions of  $Te_{ON}$  and  $Te_{OFF}$

Figure 4: FSK Level Detector Operation

#### 4.6 FSK Demodulator

This block converts the 1200bps FSK input signal to a logic level received data signal which is output via the RXD pin as long as the Data Retiming function is not enabled (see section 4.8). This output does not depend on the state of the DET output.

When the Rx 1200bps mode is 'Off' or in 'ZP' the DET and RXD pins are held low.

Note that in the absence of a valid FSK signal, the demodulator may falsely interpret speech or other extraneous signals as data. For this reason it is advised that the RXD pin is read only when data is expected.

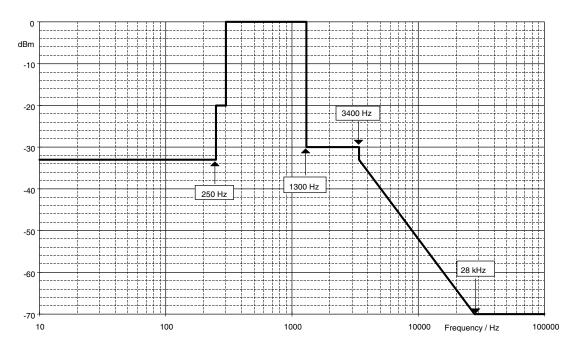

#### 4.7 FSK Modulator and Transmit Filter

These blocks produce a tone according to the TXD, M0 and M1 inputs as shown in the table below, assuming data retiming is not being used:

| M1 | MO | TXD = 0            | TXD = 1 |

|----|----|--------------------|---------|

| 1  | 1  | -                  | -       |

| 1  | 0  | 0Hz <sup>[1]</sup> | 387Hz   |

| 0  | 0  | 487Hz              | 387Hz   |

| 0  | 1  | 2200Hz             | 1200Hz  |

Note: [1] TXOUT held at approx.  $V_{DD}/2$ .

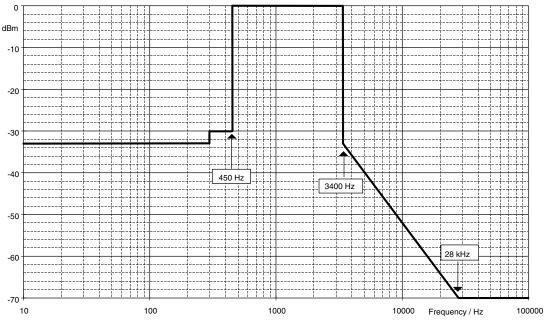

When modulated at the appropriate baud rates, the Transmit Filter and associated external components (see section 5.1) limit the FSK out of band energy sent to the line in accordance with Figure 5 and Figure 6, assuming that the signal on the line is at -6dBm or less.

Figure 5: Tx limits at 5bps and 150bps rate

Figure 6: Tx limits at 1200bps rate

#### 4.8 Rx Data Retiming

This function may be used when the received data consists of 1200bps asynchronous characters, each character consisting of one start bit followed by a minimum of 9 formatted bits as shown in the table below. Note: Rx Data Retiming is not supported for data rates exceeding 1212bps.

| Data bits | Parity bits | Stop bits |

|-----------|-------------|-----------|

| 7         | 0           | ≥2        |

| 7         | 1           | ≥ 1       |

| 8         | 0           | ≥ 1       |

| 8         | 1           | ≥ 1       |

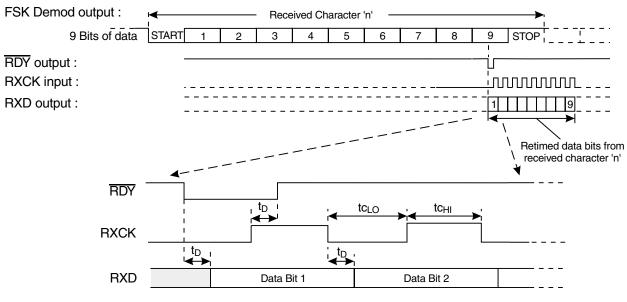

| 9         | 0           | ≥ 1       |

The Data Retiming block, when enabled in receive mode, extracts the first 9 bits of each character following the start bit from the received asynchronous data stream, and presents them to the  $\mu$ C under the control of strobe pulses applied to the CLK input. The timing of these pulses is not critical and they may easily be generated by a simple software loop. This facility removes the need for a UART in the  $\mu$ C without incurring an excessive software overhead.

The receive retiming block consists of two 9-bit shift registers, the input of the first is connected to the output of the FSK demodulator and the output of the second is connected to the RXD pin. The first register is clocked by an internally generated signal that stores the 9 received bits following the timing reference of a high to low transition at the output of the FSK demodulator. When the 9th bit is clocked into the first register these 9 bits are transferred to the second register, a new stop-start search is initiated and the CLK input is sampled. If the CLK input is low at this time the RDY pin is pulled low and the first received bit is output on the RXD pin. The CLK pin should then be pulsed high 9 times, the first 8 high to low transitions will be used by the device to clock out the bits in the second register. The RDY output is cleared the first time the CLK input goes high. At the end of the 9th pulse the RXD pin will be connected to the FSK demodulator output.

So to use the Data Retiming function, the CLK input should be kept low until the  $\overline{RDY}$  output goes low; if the Data Retiming function is not required the CLK input should be kept high at all times.

Bell 202 Compatible Modem

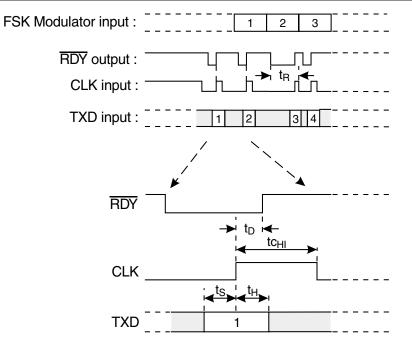

The only restrictions on the timing of the CLK waveform are those shown in Figure 7 and the need to complete the transfer of all nine bits into the  $\mu$ C within the time of a complete character at 1200bps. See Section 6.2 for Timing specifications.

$t_D$  = Internal MX614 delay,  $t_{CHI}$  = CLK high time,  $t_{CLO}$  = CLK low time

Figure 7: FSK Operation with Rx Data Retiming

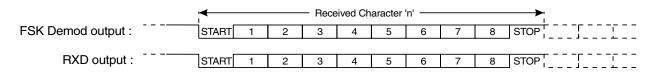

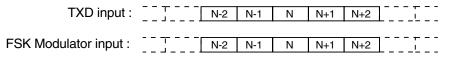

Note that, if enabled, the Data Retiming block may interpret speech or other signals as random characters. If the Data Retiming facility is not required, the CLK input to the MX614 should be kept high at all times. The asynchronous data from the FSK Demodulator will then be connected directly to the RXD output pin, and the RDY output will not be activated by the FSK signal. This case is illustrated by the example in Figure 8.

## 4.9 Tx Data Retiming

The Data Retiming block, when enabled in 1200bps transmit mode, requires the controlling  $\mu$ C to load one bit at a time into the device by a pulse applied to the CLK input. The timing of this pulse is not critical and it may easily be generated by a simple software loop. This facility removes the need for a UART in the  $\mu$ C without incurring an excessive software overhead. Note: Tx Data Retiming is not supported for data rates exceeding 1212bps.

The Tx re-timing circuit consists of two 1-bit registers in series, the input of the first is connected to the TXD pin and the output of the second feeds the FSK modulator. The second register is clocked by an internally generated 1200Hz signal and when this occurs the CLK input is sampled. If the CLK input is high the TXD pin directly controls the FSK modulator, if the CLK input is low the FSK modulator is controlled by the output of the second register and the RDY pin is pulled low. The RDY output is reset by a high level on the CLK input pin. A low to high change on the CLK input pin will latch the data from the TXD input pin into the first register ready for transfer to the second register when the internal 1200Hz signal next occurs.

So to use the retiming option the CLK input should be held low until the  $\overline{RDY}$  output is pulled low. When the  $\overline{RDY}$  pin goes low the next data bit should be applied at the TXD input and the CLK input pulled high and then low within the time limits set out in Figure 9. See Section 6.2 for Timing specifications.

11

$t_D$  = Internal MX614 delay,  $t_R$  =  $\overrightarrow{RDY}$  low to CLK going low,  $t_S$  = data set up time  $t_{CHI}$  = CLK high time,  $t_H$  = data hold time

#### Figure 9: FSK Operation with Tx Data Retiming

To ensure synchronization between the controlling device and the MX614 when entering Tx retiming mode the TXD pin must be held at a constant logic level from when the CLK pin is first pulled low to the end of loading in the second retimed bit. Similarly when exiting Tx retiming mode the TXD pin should be held at the same logic level as the last retimed bit for at least 2 bit times after the CLK line is pulled high.

If the data retiming facility is not required, the CLK input to the MX614 should be kept high at all times. The asynchronous data to the FSK modulator will then be connected directly to the TXD input pin. This is illustrated in Figure 10 and will also be the case when transmitting 5bps or 150bps data which has no retime option.

Figure 10: FSK Operation without Tx Data Retiming (CLK always high)

# 5. Application

## 5.1 Line Interface

The signals on the telephone line are not suitable for direct connection to the MX614. A Line Interface circuit is required to:

- Provide high voltage and dc isolation

- Attenuate the Tx signal present at the Rx input

- Provide the low impedance drive necessary for the line

- Filter the Tx and Rx signals

Figure 11: Line Interface Circuit

#### Line Interface Notes:

- 1. The components 'Z' between points B and C should match the line impedance.

- 2. Device A2 must be able to drive 'Z' and the line.

L

- 3. R2: For optimum results R2 should be set so that the gain is  $V_{DD}/5.0$ , i.e. R2 = 100k $\Omega$  at  $V_{DD}$  = 5.0V, rising to 150k $\Omega$  at  $V_{DD}$  = 3.3V.

- 4. R3: The levels in dB (relative to a 775mV<sub>RMS</sub> signal) at 'A', 'B' and 'C' in the line interface circuit are:

Example:

| V <sub>DD</sub> | ' <b>A</b> ' | R3    | 'B'    | 'C'    |

|-----------------|--------------|-------|--------|--------|

| 3.3V            | -3.6dB       | 100kΩ | -3.6dB | -9.6dB |

| 5.0V            | 0dB          | 150kΩ | -3.5dB | -9.5dB |

## 6. Performance Specification

#### 6.1 Electrical Performance

#### **Absolute Maximum Ratings**

Exceeding these maximum ratings can result in damage to the device.

| General                                                      | Min. | Max.                  | Units            |

|--------------------------------------------------------------|------|-----------------------|------------------|

| Supply (V <sub>DD</sub> - V <sub>SS</sub> )                  | -0.3 | 7.0                   | V                |

| Voltage on any pin to $V_{SS}$                               | -0.3 | V <sub>DD</sub> + 0.3 | V                |

| Current into or out of and pins                              |      |                       |                  |

| V <sub>DD</sub>                                              | -30  | 30                    | mA               |

| V <sub>SS</sub>                                              | -30  | 30                    | mA               |

| Any other pins                                               | -20  | 20                    | mA               |

| DW / PDIP Packages                                           |      |                       |                  |

| Total Allowable Power Dissipation at $T_{AMB} = 25^{\circ}C$ |      | 800                   | mW               |

| Derating above 25°C                                          |      | 13                    | mW/°C above 25°C |

| Storage Temperature                                          | -55  | 125                   | ۵°               |

| Operating Temperature                                        | -40  | 85                    | ۵°               |

#### **Operating Limits**

Correct operation of the device outside these limits is not implied.

|                                             | Notes | Min.     | Max.     | Units |

|---------------------------------------------|-------|----------|----------|-------|

| Supply (V <sub>DD</sub> - V <sub>SS</sub> ) |       | 3.0      | 5.5      | V     |

| Operating Temperature                       |       | -40      | 85       | О°    |

| Xtal Frequency                              | 1     | 3.575965 | 3.583125 | MHz   |

#### **Operating Limits Notes:**

1. A crystal frequency of 3.579545MHz ±0.1% is required for correct FSK operation.

#### 14

#### **Operating Characteristics**

For the following conditions unless otherwise specified:

$V_{DD}$  = 3.3V at  $T_{AMB}$  = 25°C Xtal Frequency = 3.579545MHz  $\pm$  0.1% 0dBV corresponds to 1.0V\_{RMS} Tx and Rx data rates = 1200bps.

|                                                                                                   | Notes | Min.                 | Тур. | Max.  | Units    |

|---------------------------------------------------------------------------------------------------|-------|----------------------|------|-------|----------|

| DC Parameters                                                                                     |       |                      |      |       |          |

| I <sub>DD</sub> (M0 = '1', M1 = '1')                                                              | 1, 2  |                      | 1.0  |       | μA       |

| $I_{DD}$ (M0 or M1 = '0') at $V_{DD}$ = 3.0V                                                      | 1     |                      | 1.0  | 1.25  | mA       |

| $I_{DD}$ (M0 or M1 = '0') at $V_{DD}$ = 5.0V                                                      | 1     |                      | 1.7  | 2.5   | mA       |

| Logic '1' Input Level                                                                             |       | 70%                  |      |       | $V_{DD}$ |

| Logic '0' Input Level                                                                             |       |                      |      | 30%   | $V_{DD}$ |

| Logic Input Leakage Current (V <sub>IN</sub> = 0 to V <sub>DD</sub> ), Excluding XTAL/CLOCK Input |       | -1.0                 |      | 1.0   | μA       |

| Output Logic '1' Level (I <sub>OH</sub> = 360μA)                                                  |       | V <sub>DD</sub> -0.4 |      |       | V        |

| Output Logic '0' Level (I <sub>OL</sub> = 360µA)                                                  |       |                      |      | 0.4   | V        |

| <b>RDY</b> Output 'off' State Current ( $V_{OUT} = V_{DD}$ )                                      |       |                      |      | 1.0   | μA       |

| FSK Demodulator                                                                                   |       |                      |      |       |          |

| Bit Rate                                                                                          | 3     | 0                    | 1200 | 1818  | Baud     |

| Mark (Logical '1') Frequency                                                                      |       | 1188                 | 1200 | 1212  | Hz       |

| Space (Logical '0') Frequency                                                                     |       | 2178                 | 2200 | 2222  | Hz       |

| Valid Input Level Range                                                                           | 4, 5  | -40.0                |      | -8.0  | dBV      |

| Maximum Twist (Mark Level wrt Space Level)                                                        |       | ±6.0                 |      |       | dB       |

| Acceptable Signal to Noise Ratio                                                                  | 6     | 20.0                 |      |       | dB       |

| Level Detector 'On' Threshold Level                                                               | 4     |                      |      | -40.0 | dBV      |

| Level Detector 'Off' to 'On' Time (Figure 4 Te <sub>ON</sub> )                                    |       |                      |      | 25.0  | ms       |

| Level Detector 'On' to 'Off' Time (Figure 4 Te <sub>OFF</sub> )                                   |       | 8.0                  |      |       | ms       |

| FSK Retiming                                                                                      |       |                      |      |       |          |

| Acceptable Rx Data Rate                                                                           |       | 1188                 | 1200 | 1212  | Baud     |

| Tx Data Rate                                                                                      |       | 1194                 |      | 1206  | Baud     |

| FSK Modulator                                                                                     |       |                      |      |       |          |

| TXOUT Level Driving $\geq 40 k\Omega$ load                                                        | 7     | -3.2                 | -2.2 | -1.2  | dBV      |

| Twist (Mark Level wrt Space Level)                                                                |       | -2.0                 | 0    | 2.0   | dB       |

| Tx 1200bps (M1 = '0', M0 = '1').                                                                  |       |                      |      |       |          |

| Bit Rate                                                                                          | 3     | 0                    | 1200 | 1818  | Baud     |

| Mark (Logical '1') Frequency                                                                      |       | 1197                 |      | 1203  | Hz       |

| Space (Logical '0') Frequency                                                                     |       | 2196                 |      | 2204  | Hz       |

| Tx 150bps (M1 = '0', M0 = '0').                                                                   |       |                      |      |       |          |

| Bit Rate                                                                                          |       | 0                    | 150  | 152   | Baud     |

| Mark (Logical '1') Frequency                                                                      |       | 385                  |      | 389   | Hz       |

| Space (Logical '0') Frequency                                                                     |       | 485                  |      | 489   | Hz       |

| Tx 5bps (M1 = '1', M0 = '0').                                                                     |       |                      |      |       |          |

| Bit Rate                                                                                          |       | 0                    | 5.0  | 5.1   | Baud     |

| Mark (Logical '1') Frequency                                                                      |       | 385                  |      | 389   | Hz       |

|                               | Notes | Min. | Тур. | Max. | Units |

|-------------------------------|-------|------|------|------|-------|

| Space (Logical '0') Frequency | 8     |      | 0    |      | Hz    |

| Input Amplifier               |       |      |      |      |       |

| Impedance (RXIN Pin)          | 9     | 10.0 |      |      | MΩ    |

| Voltage Gain                  | 9     |      | 500  |      | V/V   |

| XTAL/CLOCK Input              |       |      |      |      |       |

| 'High' Pulse Width            | 10    | 100  |      |      | ns    |

| 'Low' Pulse Width             | 10    | 100  |      |      | ns    |

#### **Operating Characteristics Notes:**

- 1. Not including any current drawn from the MX614 pins by external circuitry other than X1, C1 and C2.

- 2. TXD, RXEQ and CLK inputs at  $V_{SS}$ , M0 and M1 inputs at  $V_{DD}$ .

- 3. Tested at 1200bps.

- 4. Measured at the Rx Input Amplifier output (pin RXAMPOUT) for 1200Hz and  $V_{DD}$ = 5.0V. The internal threshold levels are proportional to  $V_{DD}$ . To cater for other supply voltages or different signal level ranges the voltage gain of the Rx Input Amplifier should be adjusted by selecting the appropriate external components as described in section 5.1.

- 5. Best 1818bps performance is achieved when the minimum Input Level is  $\geq$  -32dBV.

- 6. Flat noise in 200 3200Hz band.

- 7. At  $V_{DD}$ = 5.0V. (-2.2dBV is equivalent to 0dBm ref. 775mV<sub>RMS</sub> into 600 $\Omega$ .)

- 8. TXOUT held at approximately  $V_{DD}/2$ .

- 9. Open loop, small signal low frequency measurements.

- 10. Timing for an external input to the XTAL/CLOCK pin.

#### 6.2 Timing

| Data and Mode Timing                  | Notes | Min. | Тур. | Max. | Units |

|---------------------------------------|-------|------|------|------|-------|

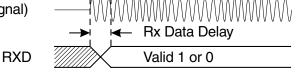

| Rx Data Delay (RXIN to RXD)           | 1, 5  |      | 2.55 |      | ms    |

| Tx Delay Data (TXD to TXOUT)          | 1, 6  |      | 0.1  |      | ms    |

| Mode change delay ZP to Tx or Rx      | 2     |      |      | 20   | ms    |

| Mode change delay Tx1200 to Rx1200    | 2     |      |      | 4.0  | ms    |

| Mode change delay Rx1200 to Tx1200    | 2     |      |      | 0.2  | ms    |

| t <sub>D</sub> = Internal MX614 delay | 3, 4  |      |      | 1    | μs    |

| tc <sub>HI</sub> = CLK High time      | 3, 4  | 1    |      |      | μs    |

| tc <sub>LO</sub> = CLK low time       | 3     | 1    |      |      | μs    |

| $t_R = RDY$ low to CLK going low      | 4     |      |      | 800  | μs    |

| t <sub>S</sub> = Data Set-up time     | 4     | 1    |      |      | μs    |

| t <sub>H</sub> = Data Hold time       | 4     | 1    |      |      | μs    |

#### **Timing Notes**

- 1. When data retiming is not enabled.

- 2. Delay from mode change to reliable data at TXOUT or RXD pins.

- 3. Reference Figure 7.

- 4. Reference Figure 9.

- 5. Reference Figure 12.

- 6. Reference Figure 13.

RXIN (FSK Signal)

Note: M0 and M1 are preset and stable.

#### Figure 12: RXIN to RXD Delay time

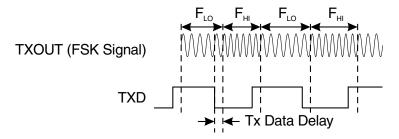

Note: M0 and M1 are preset and stable.  $F_{LO}$  and  $F_{HI}$  are the two FSK signaling frequencies.

#### Figure 13: TXD to TXOUT Delay time

#### MX614 PRELIMINARY INFORMATION

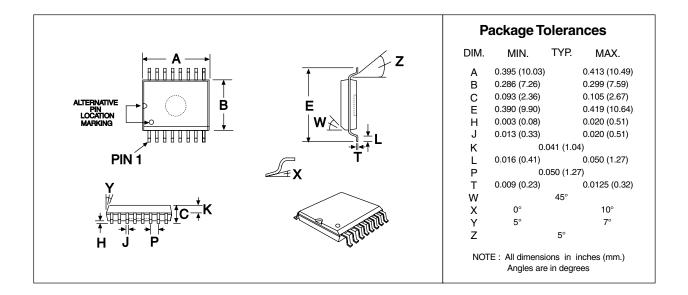

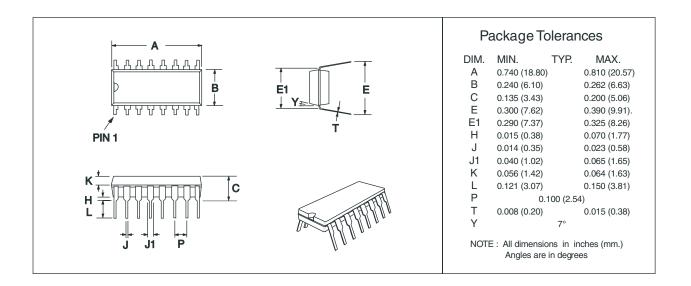

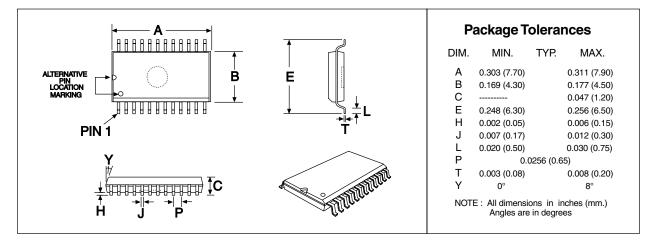

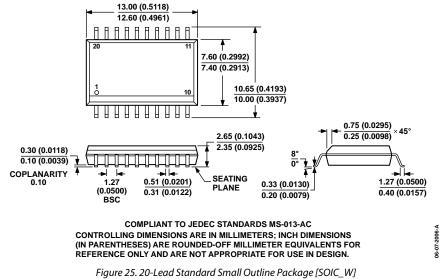

### 6.3 Packaging

Figure 14: 16-pin SOIC Mechanical Outline: Order as part no. MX614DW

Figure 15: 16-pin PDIP Mechanical Outline: Order as part no. MX614P

Figure 16 : 24-pin TSSOP Mechanical Outline: Order as part no. MX614TN

## **CML Product Data**

In the process of creating a more global image, the three standard product semiconductor companies of CML Microsystems Plc (*Consumer Microcircuits Limited (UK), MX-COM, Inc (USA) and CML Microcircuits (Singapore) Pte Ltd)* have undergone name changes and, whilst maintaining their separate new names (*CML Microcircuits (UK) Ltd, CML Microcircuits (USA) Inc and CML Microcircuits (Singapore) Pte Ltd*), now operate under the single title CML Microcircuits.

These companies are all 100% owned operating companies of the CML Microsystems Plc Group and these changes are purely changes of name and do not change any underlying legal entities and hence will have no effect on any agreements or contacts currently in force.

#### **CML Microcircuits Product Prefix Codes**

Until the latter part of 1996, the differentiator between products manufactured and sold from MXCOM, Inc. and Consumer Microcircuits Limited were denoted by the prefixes MX and FX respectively. These products use the same silicon etc. and today still carry the same prefixes. In the latter part of 1996, both companies adopted the common prefix: CMX.

This notification is relevant product information to which it is attached.

#### CML Microcircuits (USA) [formerly MX-COM, Inc.] Product Textual Marking

On CML Microcircuits (USA) products, the **'MX-COM'** textual logo is being replaced by a **'CML'** textual logo.

Company contact information is as below:

Oval Park, Langford, Maldon, Essex, CM9 6WG, England Tel: +44 (0)1621 875500 Fax: +44 (0)1621 875600 uk.sales@cmlmicro.com www.cmlmicro.com

COMMUNICATION SEMICONDUCTORS

4800 Bethania Station Road, Winston-Salem, NC 27105, USA Tel: +1 336 744 5050, 0800 638 5577 Fax: +1 336 744 5054 us.sales@cmlmicro.com www.cmlmicro.com

No 2 Kallang Pudding Road, 09-05/ 06 Mactech Industrial Building, Singapore 349307 Tel: +65 7450426 Fax: +65 7452917 sg.sales@cmlmicro.com www.cmlmicro.com

# **Data Sheet**

# **RS-232 Line Driver/Receiver**

# **ADM3251E**

#### **FEATURES**

2.5 kV fully isolated (power and data) RS-232 transceiver isoPower integrated, isolated dc-to-dc converter 460 kbps data rate 1 Tx and 1 Rx Meets EIA/TIA-232E specifications ESD protection on RIN and TOUT pins ±8 kV: contact discharge ±15 kV: air gap discharge 0.1 µF charge pump capacitors High common-mode transient immunity: >25 kV/µs Safety and regulatory approvals **UL** recognition 2500 V rms for 1 minute per UL 1577 **VDE** Certificate of Conformity DIN EN 60747-5-2 (VDE 0884 Teil 2): 2003-01 **CSA Component Acceptance Notice #5A** Operating temperature range: -40°C to +85°C Wide body, 20-lead SOIC package

#### **APPLICATIONS**

High noise data communications Industrial communications General-purpose RS232 data links Industrial/telecommunications diagnostic ports **Medical equipment**

#### **GENERAL DESCRIPTION**

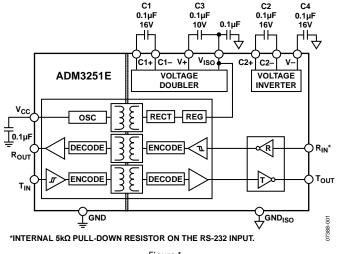

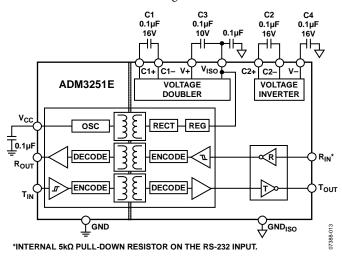

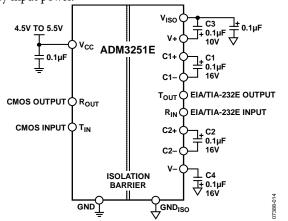

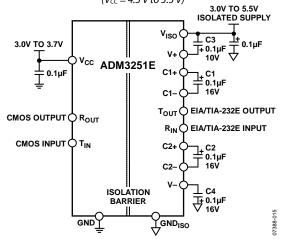

The ADM3251E<sup>1</sup> is a high speed, 2.5 kV fully isolated, singlechannel RS-232/V.28 transceiver device that operates from a single 5 V power supply. Due to the high ESD protection on the R<sub>IN</sub> and T<sub>OUT</sub> pins, the device is ideally suited for operation in electrically harsh environments or where RS-232 cables are frequently being plugged and unplugged.

The ADM3251E incorporates dual-channel digital isolators with isoPower<sup>™</sup> integrated, isolated power. There is no requirement to use a separate isolated dc-to-dc converter. Chip-scale transformer iCoupler® technology from Analog Devices, Inc., is used both for the isolation of the logic signals as well as for the integrated dc-to-dc converter. The result is a total isolation solution.

The ADM3251E contains isoPower technology that uses high frequency switching elements to transfer power through the

FUNCTIONAL BLOCK DIAGRAM

Isolated, Single-Channel

Figure 1.

transformer. Special care must be taken during printed circuit board (PCB) layout to meet emissions standards. Refer to Application Note AN-0971, Control of Radiated Emissions with isoPower Devices, for details on board layout considerations.

The ADM3251E conforms to the EIA/TIA-232E and ITU-T V. 28 specifications and operates at data rates up to 460 kbps.

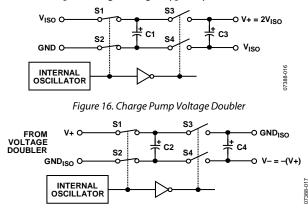

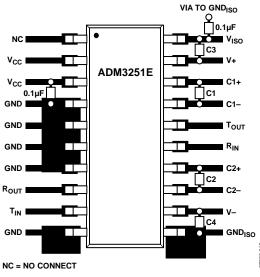

Four external 0.1 µF charge pump capacitors are used for the voltage doubler/inverter, permitting operation from a single 5 V supply.

The ADM3251E is available in a 20-lead, wide body SOIC package and is specified over the  $-40^{\circ}$ C to  $+85^{\circ}$ C temperature range.

<sup>1</sup> Protected by U.S. Patents 5,952,849; 6,873,065; and 7,075,329.

#### Rev. G

**Document Feedback**

Information furnished by Analog Devices is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties that may result from its use. Specifications subject to change without notice. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices. Trademarks and registered trademarks are the property of their respective owners.

# ADM3251E\* PRODUCT PAGE QUICK LINKS

Last Content Update: 02/23/2017

## COMPARABLE PARTS 🖵

View a parametric search of comparable parts.

## EVALUATION KITS

ADM3251E Evaluation board

## **DOCUMENTATION**

#### **Application Notes**

• AN-740: iCoupler Isolation in RS-232 Applications

#### Data Sheet

ADM3251E: Isolated, Single-Channel RS-232 Line Driver/ Receiver Data Sheet

#### **User Guides**

- UG-120: Standard Evaluation Kit User Guide for the ADM3251E

- UG-124: EMI optimized evaluation kit user guide for the ADM3251E

- UG-181: PLC Demo System, Industrial Process Control Demo System

## REFERENCE MATERIALS

#### Press

• Analog Devices Achieves Major Milestone by Shipping 1 Billionth Channel of iCoupler Digital Isolation

#### **Product Selection Guide**

• Digital Isolator Product Selection and Resource Guide

#### **Solutions Bulletins & Brochures**

• RS-232 Transceivers Applications Bulletin (Summer 2008)

#### **Technical Articles**

- Inside iCoupler<sup>®</sup> Technology:ADuM347x PWM Controller and Transformer Driver with Quad-Channel Isolators Design Summary

- NAppkin Note: Lowering the Power of the ADuM524x

- Part 1: Simplifying Design of Industrial Process-Control Systems with PLC Evaluation Boards

- Part 2: Simplifying Design of Industrial Process-Control Systems with PLC Evaluation Boards

## DESIGN RESOURCES

- ADM3251E Material Declaration

- PCN-PDN Information

- Quality And Reliability

- Symbols and Footprints

## DISCUSSIONS

View all ADM3251E EngineerZone Discussions.

## SAMPLE AND BUY

Visit the product page to see pricing options.

## TECHNICAL SUPPORT

Submit a technical question or find your regional support number.

# DOCUMENT FEEDBACK 🖵

Submit feedback for this data sheet.

# TABLE OF CONTENTS

| Features                                               |

|--------------------------------------------------------|

| Applications1                                          |

| Functional Block Diagram1                              |

| General Description                                    |

| Revision History                                       |

| Specifications                                         |

| Package Characteristics5                               |

| Regulatory Information 5                               |

| Insulation and Safety-Related Specifications5          |

| DIN EN 60747-5-2 (VDE 0884 TEIL 2): 2003-01 Insulation |

| Characteristics                                        |

| Absolute Maximum Ratings7                              |

| ESD Caution7                                           |

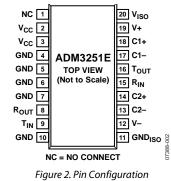

| Pin Configuration and Function Descriptions            |

| Typical Performance Characteristics                    |

#### **REVISION HISTORY**

#### 6/12—Rev. E to Rev. F

| Changes to Endnote 1 in Table 4                          | 5 |

|----------------------------------------------------------|---|

| Added DC Correctness and Magnetic Field Immunity         |   |

| Section1                                                 | 3 |

| Added Figure 22 and Figure 23; Renumbered Sequentially 1 | 4 |

| Updated Outline Dimensions and Changes to                |   |

| Ordering Guide1                                          | 5 |

#### 5/10-Rev. D to Rev. E

| Changes to Features Section | . 1 |

|-----------------------------|-----|

| Changes to Table 4          | . 5 |

#### 3/10-Rev. C to Rev. D

| Changes to Features and General Description Sections   |

|--------------------------------------------------------|

| Changes to Table 4 and Table 5                         |

| Changed DIN V VDE V 0884-10 (VDE V 0884-10):2006-12    |

| Insulation Characteristics (Pending) Heading to DIN EN |

| 60747-5-2 (VDE 0884 Teil 2): 2003-01 Insulation        |

| Characteristics                                        |

| Theory of Operation                        | 11 |

|--------------------------------------------|----|

| Isolation of Power and Data                | 11 |

| Charge Pump Voltage Converter              | 12 |

| 5.0 V Logic to EIA/TIA-232E Transmitter    | 12 |

| EIA/TIA-232E to 5 V Logic Receiver         | 12 |

| High Baud Rate                             | 12 |

| Thermal Analysis                           | 12 |

| Insulation Lifetime                        | 12 |

| Applications Information                   | 13 |

| PCB Layout                                 | 13 |

| Example PCB for Reduced EMI                | 13 |

| DC Correctness and Magnetic Field Immunity | 13 |

| Isolated Power Supply Circuit              | 14 |

| Outline Dimensions                         | 15 |

| Ordering Guide                             | 15 |

| Changes to Pollution Degree and Input-to-Output Test Voltage | e  |

|--------------------------------------------------------------|----|

| Parameters, Table 6                                          | .6 |

| Added Applications Information Section and Example PCB for   |    |

| Reduced EMI Section; Added Table 9 and Table 10;             |    |

| Renumbered Sequentially 1                                    | 13 |

| Changes to PCB Layout Section 1                              | 13 |

| Added Isolated Power Supply Circuit Section, and Figure 22;  |    |

| Renumbered Sequentially 1                                    | 14 |

|                                                              |    |

#### 1/10-Rev. B to Rev. C

| Changes to Table 4                                                     | 5  |

|------------------------------------------------------------------------|----|

| 11/09—Rev. A to Rev. B                                                 |    |

| Changes to Figure 1                                                    | 1  |

| Changed to Primary Side Supply Input Current, I <sub>CC(DISABLE)</sub> |    |

| Maximum Limit to 2.5 mA                                                | 4  |

| Changes to Table 4                                                     | 5  |

| Changes to Figure 13                                                   | 11 |

#### 9/08—Rev. 0 to Rev. A

| Changes to Timing Parameters in Table 1 | . 3 |

|-----------------------------------------|-----|

| Changes to Timing Parameters in Table 2 | . 4 |

| Changes to Ordering Guide               | 14  |

#### 7/08—Revision 0: Initial Version

# **SPECIFICATIONS**

All voltages are relative to their respective ground; all minimum/maximum specifications apply over the entire recommended operating range;  $T_A = 25^{\circ}$ C and  $V_{CC} = 5.0$  V (dc-to-dc converter enabled), unless otherwise noted.

| Table 1.                                                                  |                                  | -         |                     |       |                                                                                                                                                                  |

|---------------------------------------------------------------------------|----------------------------------|-----------|---------------------|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Parameter                                                                 | Min                              | Тур       | Max                 | Unit  | Test Conditions/Comments                                                                                                                                         |

| DC CHARACTERISTICS                                                        |                                  |           |                     |       |                                                                                                                                                                  |

| V <sub>CC</sub> Operating Voltage Range                                   | 4.5                              |           | 5.5                 | V     |                                                                                                                                                                  |

| DC-to-DC Converter Enable Threshold, V <sub>CC(ENABLE)</sub> <sup>1</sup> | 4.5                              |           |                     | V     |                                                                                                                                                                  |

| DC-to-DC Converter Disable Threshold, V <sub>CC(DISABLE)</sub> 1          |                                  |           | 3.7                 | V     |                                                                                                                                                                  |

| DC-to-DC Converter Enabled                                                |                                  |           |                     |       |                                                                                                                                                                  |

| Input Supply Current, I <sub>CC(ENABLE)</sub>                             |                                  |           | 110                 | mA    | $V_{CC} = 5.5 V$ , no load                                                                                                                                       |

|                                                                           |                                  |           | 145                 | mA    | $V_{CC} = 5.5 \text{ V}, \text{ R}_{L} = 3 \text{ k}\Omega$                                                                                                      |

| V <sub>ISO</sub> Output <sup>2</sup>                                      |                                  | 5.0       |                     | V     | $I_{ISO} = 0 \ \mu A$                                                                                                                                            |

| LOGIC                                                                     |                                  |           |                     |       |                                                                                                                                                                  |

| Transmitter Input, T <sub>IN</sub>                                        |                                  |           |                     |       |                                                                                                                                                                  |

| Logic Input Current, ITIN                                                 | -10                              | +0.01     | +10                 | μΑ    |                                                                                                                                                                  |

| Logic Low Input Threshold, V <sub>TINL</sub>                              |                                  |           | 0.3 V <sub>CC</sub> | V     |                                                                                                                                                                  |

| Logic High Input Threshold, VTINH                                         | 0.7 Vcc                          |           | • ((                | v     |                                                                                                                                                                  |

| Receiver Output, Rout                                                     |                                  |           |                     |       |                                                                                                                                                                  |

| Logic High Output, NouTH                                                  | Vcc – 0.1                        | Vcc       |                     | v     | I <sub>ROUTH</sub> = -20 μA                                                                                                                                      |

|                                                                           | $V_{CC} = 0.1$<br>$V_{CC} = 0.5$ | Vcc – 0.3 |                     | v     | $I_{\text{ROUTH}} = -20 \mu\text{A}$                                                                                                                             |

| Logic Low Output, VROUTL                                                  | V(( - 0.5                        | 0.0       | 0.1                 | v     | $I_{ROUTH} = -4 IIIA$<br>$I_{ROUTH} = 20 \mu\text{A}$                                                                                                            |

|                                                                           |                                  | 0.0       | 0.1                 | v     | $I_{ROUTH} = 20 \mu A$                                                                                                                                           |

| RS-232                                                                    |                                  | 0.5       | 0.4                 | v     | IROUTH = 4 IIIA                                                                                                                                                  |

|                                                                           |                                  |           |                     |       |                                                                                                                                                                  |

| Receiver, R <sub>IN</sub>                                                 | 20                               |           | . 20                |       |                                                                                                                                                                  |

| EIA-232 Input Voltage Range <sup>3</sup>                                  | -30                              | 2.0       | +30                 | V     |                                                                                                                                                                  |

| EIA-232 Input Threshold Low                                               | 0.6                              | 2.0       |                     | V     |                                                                                                                                                                  |

| EIA-232 Input Threshold High                                              |                                  | 2.1       | 2.4                 | V     |                                                                                                                                                                  |

| EIA-232 Input Hysteresis                                                  |                                  | 0.1       |                     | V     |                                                                                                                                                                  |

| EIA-232 Input Resistance                                                  | 3                                | 5         | 7                   | kΩ    |                                                                                                                                                                  |

| Transmitter, Tout                                                         |                                  |           |                     |       |                                                                                                                                                                  |

| Output Voltage Swing (RS-232)                                             | ±5                               | ±5.7      |                     | V     | $R_L = 3 k\Omega$ to GND                                                                                                                                         |

| Transmitter Output Resistance                                             | 300                              |           |                     | Ω     | $V_{ISO} = 0 V$                                                                                                                                                  |

| Output Short-Circuit Current (RS-232)                                     |                                  | ±12       |                     | mA    |                                                                                                                                                                  |

| TIMING CHARACTERISTICS                                                    |                                  |           |                     |       |                                                                                                                                                                  |

| Maximum Data Rate                                                         | 460                              |           |                     | kbps  | $R_L$ = 3 k $\Omega$ to 7 k $\Omega$ , $C_L$ = 50 pF to 1000 pF                                                                                                  |

| Receiver Propagation Delay                                                |                                  |           |                     |       |                                                                                                                                                                  |

| t <sub>PHL</sub>                                                          |                                  | 190       |                     | ns    |                                                                                                                                                                  |

| t <sub>PLH</sub>                                                          |                                  | 135       |                     | ns    |                                                                                                                                                                  |

| Transmitter Propagation Delay                                             |                                  | 650       |                     | ns    | $R_L = 3 \text{ k}\Omega, C_L = 1000 \text{ pF}$                                                                                                                 |

| Transmitter Skew                                                          |                                  | 80        |                     | ns    |                                                                                                                                                                  |

| Receiver Skew                                                             |                                  | 70        |                     | ns    |                                                                                                                                                                  |

| Transition Region Slew Rate <sup>3</sup>                                  | 5.5                              | 10        | 30                  | V/µs  | $\begin{array}{l} +3 \ V \ to \ -3 \ V \ or \ -3 \ V \ to \ +3 \ V, \ V_{CC} = +3.3 \ V \\ R_L = 3 \ k\Omega, \ C_L = 1000 \ pF, \ T_A = 25^\circ C \end{array}$ |

| AC SPECIFICATIONS                                                         |                                  |           |                     |       |                                                                                                                                                                  |

| Output Rise/Fall Time, t <sub>R</sub> /t <sub>F</sub> (10% to 90%)        |                                  | 2.3       |                     | ns    | $C_L = 15 \text{ pF}$ , CMOS signal levels                                                                                                                       |

| Common-Mode Transient Immunity at Logic High Output <sup>4</sup>          | 25                               |           |                     | kV/μs | $V_{CM} = 1$ kV, transient magnitude = 800 V                                                                                                                     |

| Common-Mode Transient Immunity at Logic Low Output <sup>4</sup>           | 25                               |           |                     | kV/μs | $V_{CM} = 1$ kV, transient magnitude = 800 V                                                                                                                     |

| , 5 1                                                                     | ł                                | ±15       |                     | kV    | Human body model air discharge                                                                                                                                   |

| ESD PROTECTION (R <sub>IN</sub> And T <sub>OUT</sub> PINS)                |                                  |           |                     |       |                                                                                                                                                                  |

$^{1}$  Enable/disable threshold is the V<sub>CC</sub> voltage at which the internal dc-to-dc converter is enabled/disabled.

$^{2}$  To maintain data sheet specifications, do not draw current from  $V_{\text{ISO}}$

<sup>3</sup> Guaranteed by design.

<sup>4</sup> V<sub>CM</sub> is the maximum common-mode voltage slew rate that can be sustained while maintaining specification-compliant operation. V<sub>CM</sub> is the common-mode potential difference between the logic and bus sides. The transient magnitude is the range over which the common mode is slewed. The common-mode voltage slew rates apply to both rising and falling common-mode voltage edges.

# ADM3251E

All voltages are relative to their respective ground; all minimum/maximum specifications apply over the entire recommended operating range;  $T_A = 25^{\circ}C$ ,  $V_{CC} = 3.3$  V (dc-to-dc converter disabled), and the secondary side is powered externally by  $V_{ISO} = 3.3$  V, unless otherwise noted.

| Parameter                                                                   | Min                   | Тур                   | Max                 | Unit  | Test Conditions/Comments                                                                                                  |

|-----------------------------------------------------------------------------|-----------------------|-----------------------|---------------------|-------|---------------------------------------------------------------------------------------------------------------------------|

| DC CHARACTERISTICS                                                          |                       |                       |                     |       |                                                                                                                           |

| V <sub>cc</sub> Operating Voltage Range                                     | 3.0                   |                       | 3.7                 | v     |                                                                                                                           |

| DC-to-DC Converter Disable Threshold, V <sub>CC(DISABLE)</sub> <sup>1</sup> |                       |                       | 3.7                 | v     |                                                                                                                           |

| DC-to-DC Converter Disabled                                                 |                       |                       |                     |       |                                                                                                                           |

| V <sub>ISO</sub> <sup>2</sup>                                               | 3.0                   |                       | 5.5                 | v     |                                                                                                                           |

| Primary Side Supply Input Current, I <sub>CC(DISABLE)</sub>                 |                       |                       | 2.5                 | mA    | No load                                                                                                                   |

| Secondary Side Supply Input Current, IISO(DISABLE)                          |                       |                       | 12                  | mA    | $V_{ISO} = 5.5 \text{ V}, \text{ R}_L = 3 \text{ k}\Omega$                                                                |

| Secondary Side Supply Input Current, IISO(DISABLE)                          |                       | 6.2                   |                     | mA    | $R_L = 3 k\Omega$                                                                                                         |

| LOGIC                                                                       |                       |                       |                     |       |                                                                                                                           |

| Transmitter Input, T <sub>IN</sub>                                          |                       |                       |                     |       |                                                                                                                           |

| Logic Input Current, ITIN                                                   | -10                   | +0.01                 | +10                 | μΑ    |                                                                                                                           |

| Logic Low Input Threshold, V <sub>TINL</sub>                                |                       |                       | 0.3 V <sub>CC</sub> | V     |                                                                                                                           |

| Logic High Input Threshold, VTINH                                           | 0.7 Vcc               |                       |                     | V     |                                                                                                                           |

| Receiver Output, R <sub>OUT</sub>                                           |                       |                       |                     |       |                                                                                                                           |

| Logic High Output, VROUTH                                                   | Vcc - 0.1             | Vcc                   |                     | V     | $I_{ROUTH} = -20 \ \mu A$                                                                                                 |

|                                                                             | V <sub>CC</sub> – 0.5 | $V_{\text{CC}} - 0.3$ |                     | V     | $I_{ROUTH} = -4 \text{ mA}$                                                                                               |

| Logic Low Output, VROUTL                                                    |                       | 0.0                   | 0.1                 | V     | $I_{ROUTH} = 20 \ \mu A$                                                                                                  |

|                                                                             |                       | 0.3                   | 0.4                 |       | $I_{ROUTH} = 4 \text{ mA}$                                                                                                |

| RS-232                                                                      |                       |                       |                     | V     |                                                                                                                           |

| Receiver, R <sub>IN</sub>                                                   |                       |                       |                     |       |                                                                                                                           |

| EIA-232 Input Voltage Range <sup>3</sup>                                    | -30                   |                       | +30                 | V     |                                                                                                                           |

| EIA-232 Input Threshold Low                                                 | 0.6                   | 1.3                   |                     | V     |                                                                                                                           |

| EIA-232 Input Threshold High                                                |                       | 1.6                   | 2.4                 | V     |                                                                                                                           |

| EIA-232 Input Hysteresis                                                    |                       | 0.3                   |                     | V     |                                                                                                                           |

| EIA-232 Input Resistance                                                    | 3                     | 5                     | 7                   | kΩ    |                                                                                                                           |

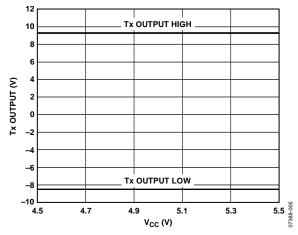

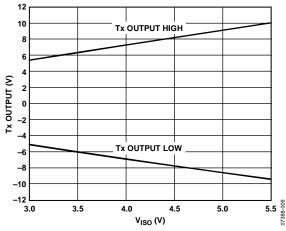

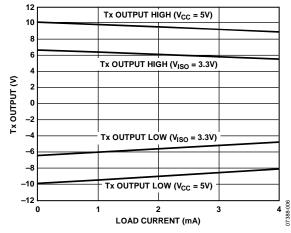

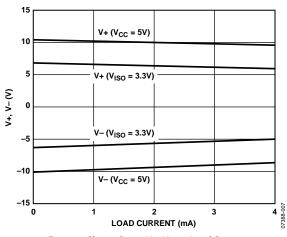

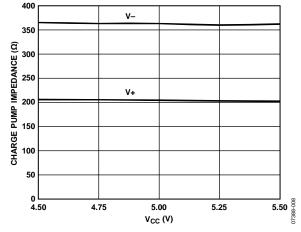

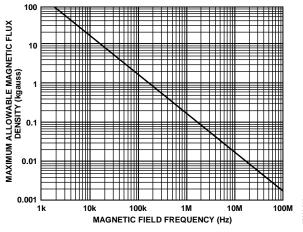

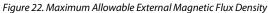

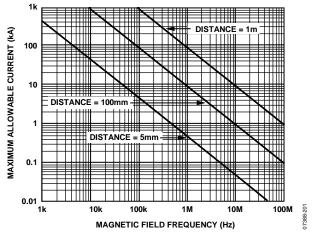

| Transmitter, T <sub>OUT</sub>                                               |                       |                       |                     |       |                                                                                                                           |